看了讓人后悔晶振PCB板設計早了

來源:http://www.lbfp.com.cn 作者:yijindz 2012年05月30

億金電子供應晶振,石英晶振,貼片晶振,進口晶振,KDS晶振,西鐵城晶振,晶振工作原理,晶振技術參數。

設計晶振時經常遇到相噪與抖動這概念,兩者之間是什么關系呢?相位噪聲和抖動是對同一種現象的兩種不同定量方式(描述)。相位噪聲是頻率域的概停飛,相位噪聲是用偏移頻率fm處1Hz帶寬內的矩形的面積,與整個功率譜曲線下包含的面積之比,單位用-dBC/Hz表示。抖動是一個時域概念,單位用pS或fS表示。

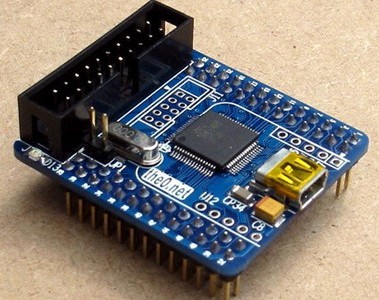

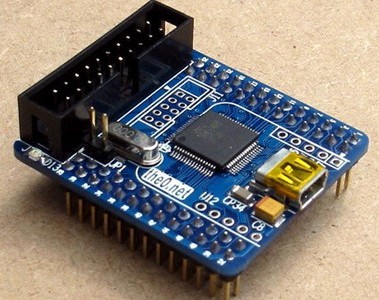

從PCB布局上考慮,晶振盡量焊在PCB上,少用插座方式,高頻信號線盡可能遠離敏感的模擬電路器件,數字地與模擬地由一點短接或通過外界接口相連例如插座,晶振應該設計在什么位置最好也是該考慮的要素,由于影響晶振短期穩定性的主要因素是溫度變化,在設計通盤布局的考慮下,盡量避免將晶振靠近機箱外殼或靠近溫度較大的部件例如風扇,還應該遠離大功率射頻器件例如射頻功放。在振動或存在加速度變化的環境下,還應該考慮晶振的受力,確保應力分布均勻,并采取有效緩沖等減振措施。電源紋波也會對晶振產生影響,通常晶振對電源的紋波和噪聲要求小于輸出電壓的1%,由于晶振內部有高精密電壓基準,其紋波抑制,負載調整率都非常優良,精度可以達到3ppm/℃,電源系統1%以內的紋波對晶振的干擾可以忽略。

設計晶振時經常遇到相噪與抖動這概念,兩者之間是什么關系呢?相位噪聲和抖動是對同一種現象的兩種不同定量方式(描述)。相位噪聲是頻率域的概停飛,相位噪聲是用偏移頻率fm處1Hz帶寬內的矩形的面積,與整個功率譜曲線下包含的面積之比,單位用-dBC/Hz表示。抖動是一個時域概念,單位用pS或fS表示。

從PCB布局上考慮,晶振盡量焊在PCB上,少用插座方式,高頻信號線盡可能遠離敏感的模擬電路器件,數字地與模擬地由一點短接或通過外界接口相連例如插座,晶振應該設計在什么位置最好也是該考慮的要素,由于影響晶振短期穩定性的主要因素是溫度變化,在設計通盤布局的考慮下,盡量避免將晶振靠近機箱外殼或靠近溫度較大的部件例如風扇,還應該遠離大功率射頻器件例如射頻功放。在振動或存在加速度變化的環境下,還應該考慮晶振的受力,確保應力分布均勻,并采取有效緩沖等減振措施。電源紋波也會對晶振產生影響,通常晶振對電源的紋波和噪聲要求小于輸出電壓的1%,由于晶振內部有高精密電壓基準,其紋波抑制,負載調整率都非常優良,精度可以達到3ppm/℃,電源系統1%以內的紋波對晶振的干擾可以忽略。

正在載入評論數據...

相關資訊

- [2025-01-06]輕松管理EMI-泰藝電子低EMI晶振(SX與...

- [2025-01-06]用于 PCIe 6.0/5.0 汽車應用的低功耗...

- [2024-12-18]Q-Tech宣布推出AXTAL GHz系列全系列

- [2024-12-07]Silicon Labs 在 ESG 方面取得卓越成...

- [2024-12-05]高頻和低抖動的 SPXO SG2016CBN,SG25...

- [2024-12-04]Statek推出 ULPXO 超低功耗晶體振蕩器...

- [2024-12-04]JT21GL(E)和JT11GL(E)是Jauch頻率產品...

- [2024-11-28]Endura 低相位噪聲 Super-TCXO

銷售代表

銷售代表